#### **Powerful of CLIQUE**

Danny Mok Altera HK FAE

You can download more files from http://www.pld.com.cn or www.fpga.com.cn

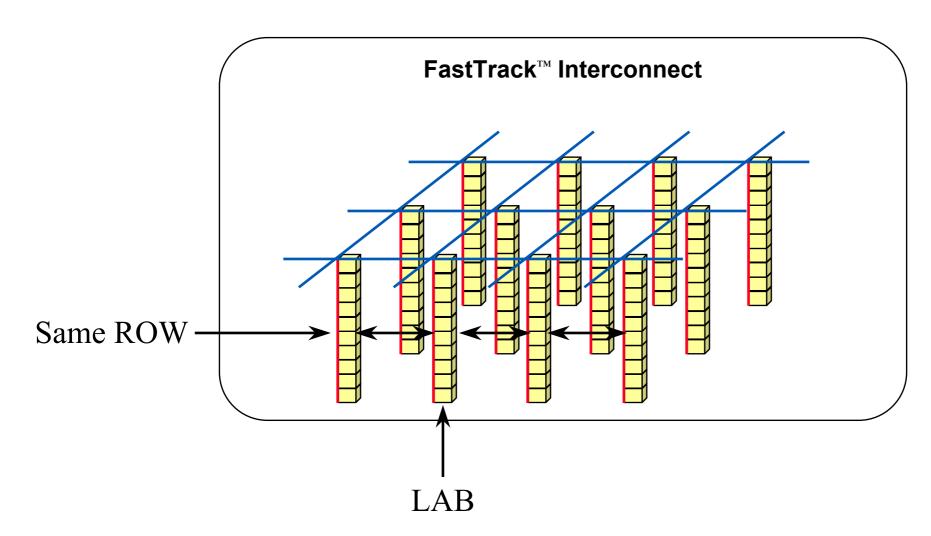

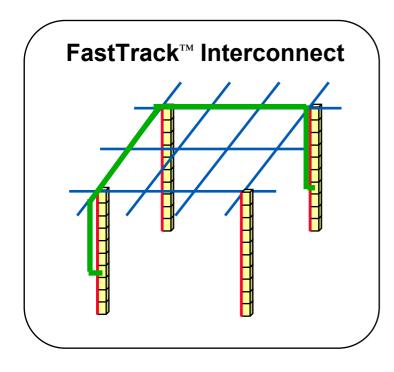

#### **Architecture of FLEX Device**

16 Column Channels Row Channels Each LE drives one row channel. LE1 LE2 to Local to Local Each LE drives up to Feedback Feedback two column channels. E...O.:- 1.71

Figure 8. LAB Connections to Row & Column Interconnect

# **Three Routing Possibility**

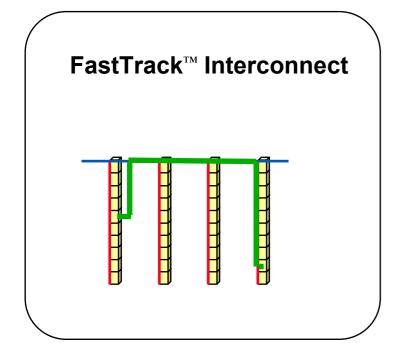

#### Routing 1

Minimum Delay LC -> LC

# **Three Routing Possibility**

#### Routing 2

Medium Delay LC -> ROW -> LC

Copyright © 1997 Altera Corporation www.FPGA.com.cn 提供

# **Three Routing Possibility**

#### Routing 3

Maximum Delay LC -> ROW -> COL -> LC

#### Which one faster?

Whichverteorum 151467445ST??

#### What is CLIQUE?

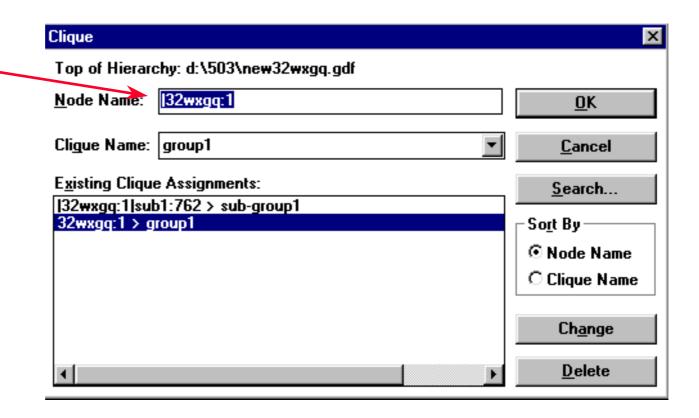

- Clique is an option which provided by Altera Max+Plus II which used to

- control the logic placement

- force the logic placement within

- the same LAB (no ROW/COLUMN trace delay) -- Highest speed

- the same ROW (no COLUMN trace delay)

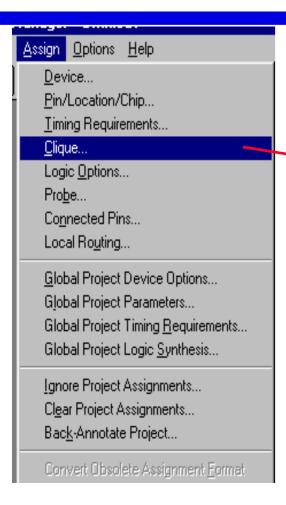

## Where is this Option?

# **Example**

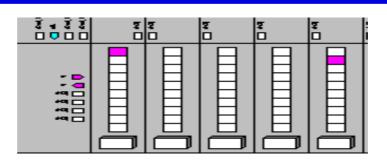

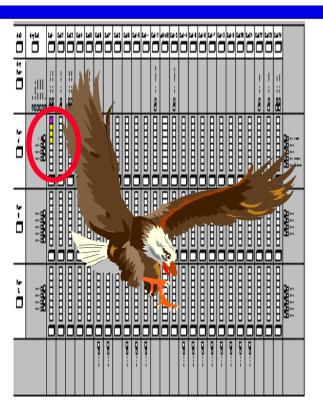

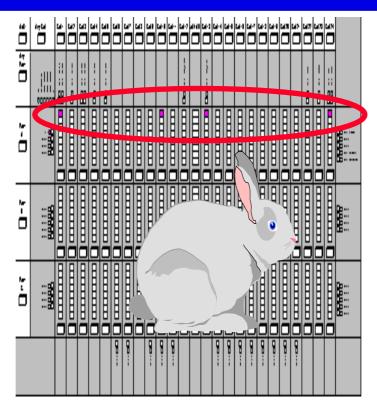

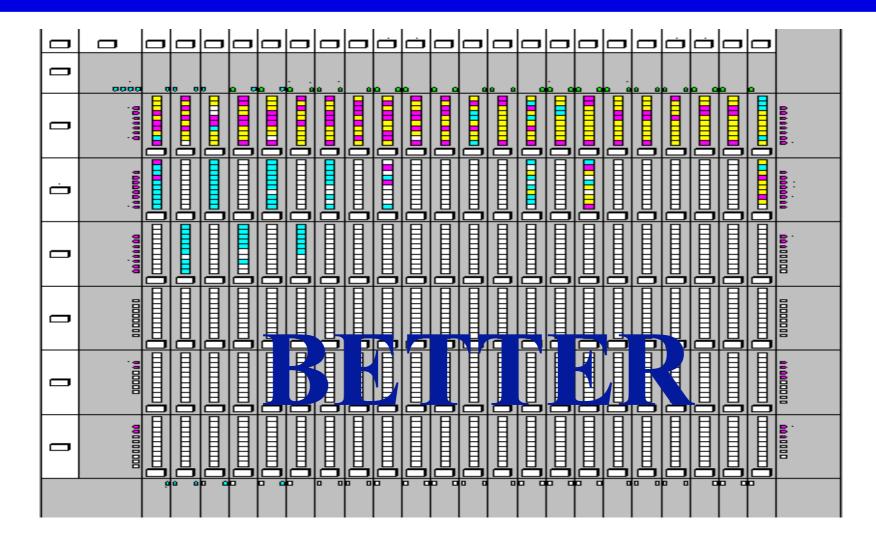

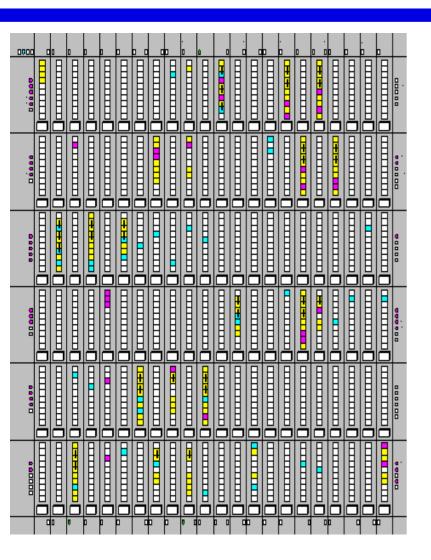

## Floorplan Look

It only run at 77.56MHz

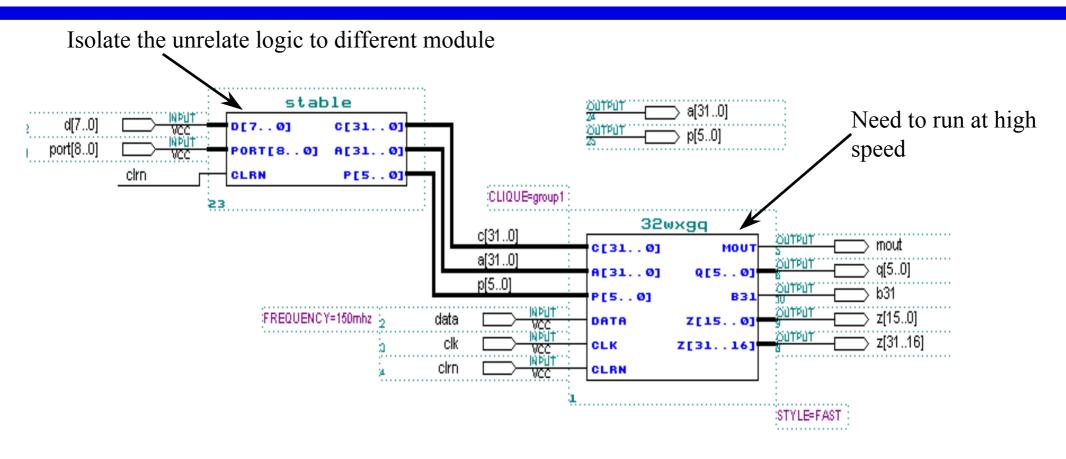

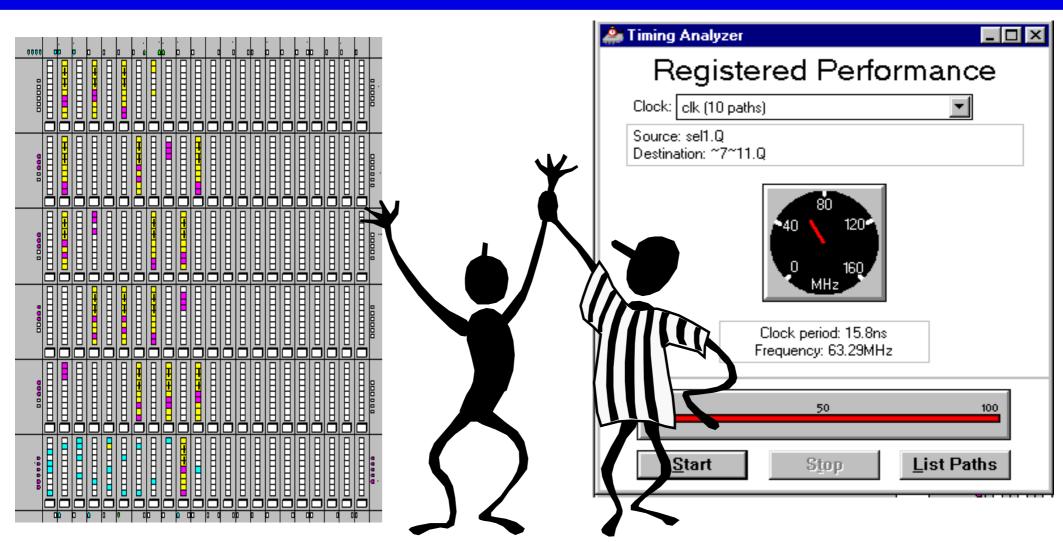

# Only a Little Bit Effort Planning

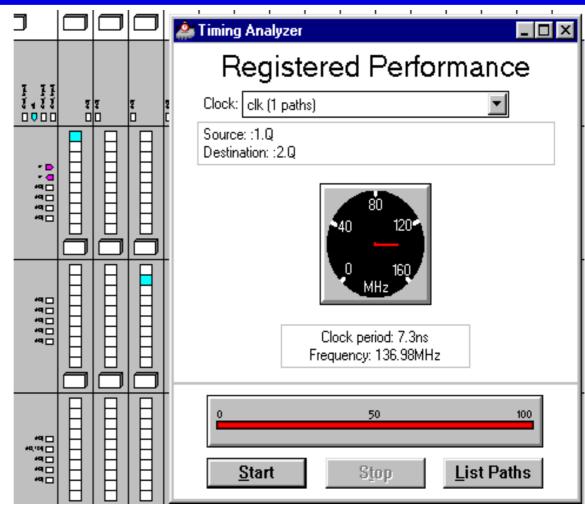

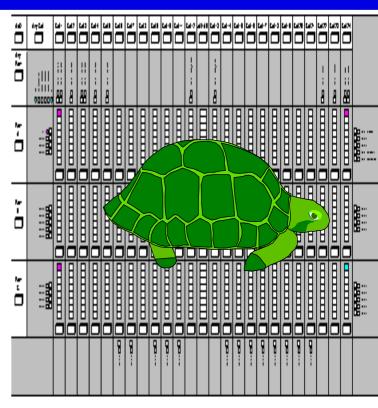

Change a flat design to 2 module

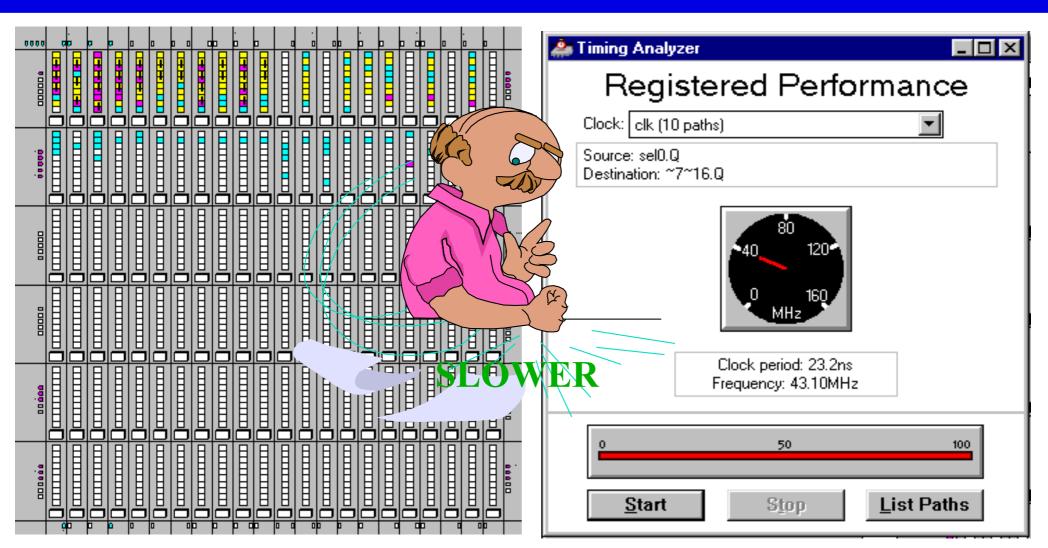

## Floorplan Look

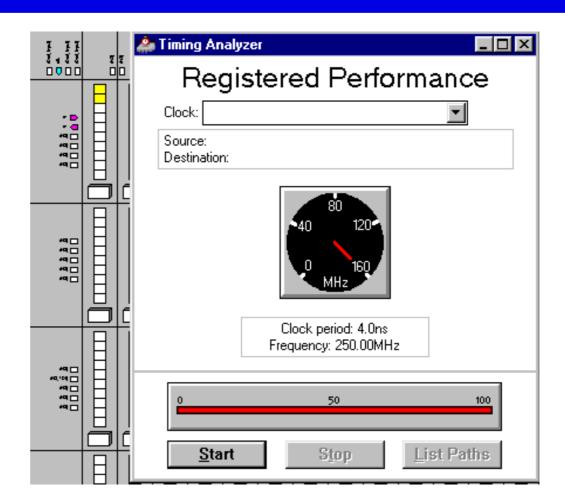

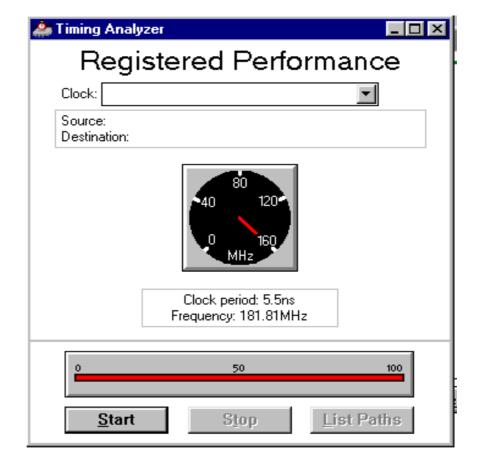

## Register Performance

No logic change, only little bit planning in advance, the speed improve from 77.56Mhz to 138.88Mhz (79% increase). Yes, it is so easy !!!!!!!

# **Use CLIQUE wisely**

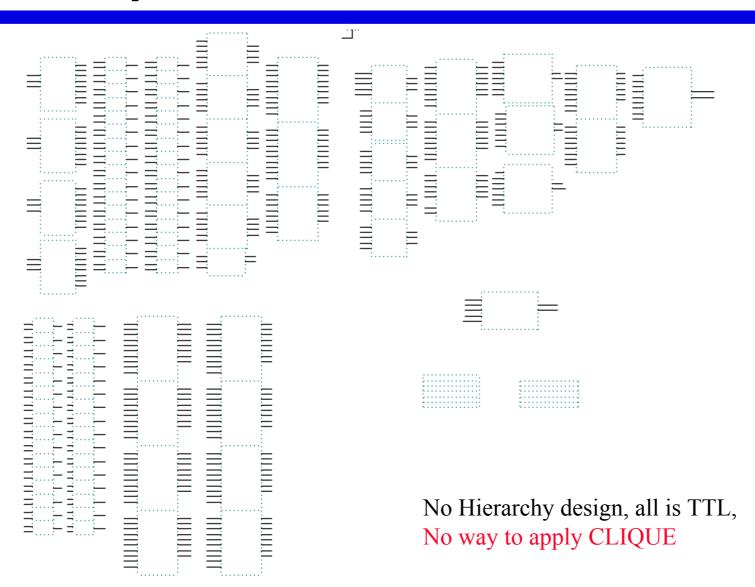

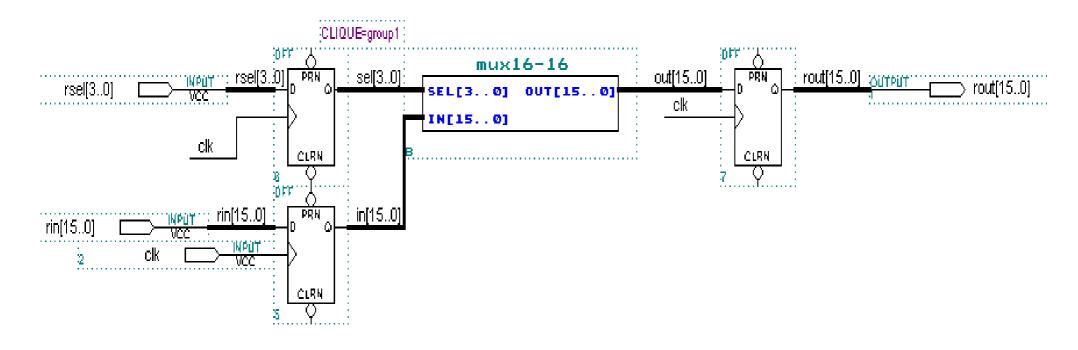

## No CLIQUE apply

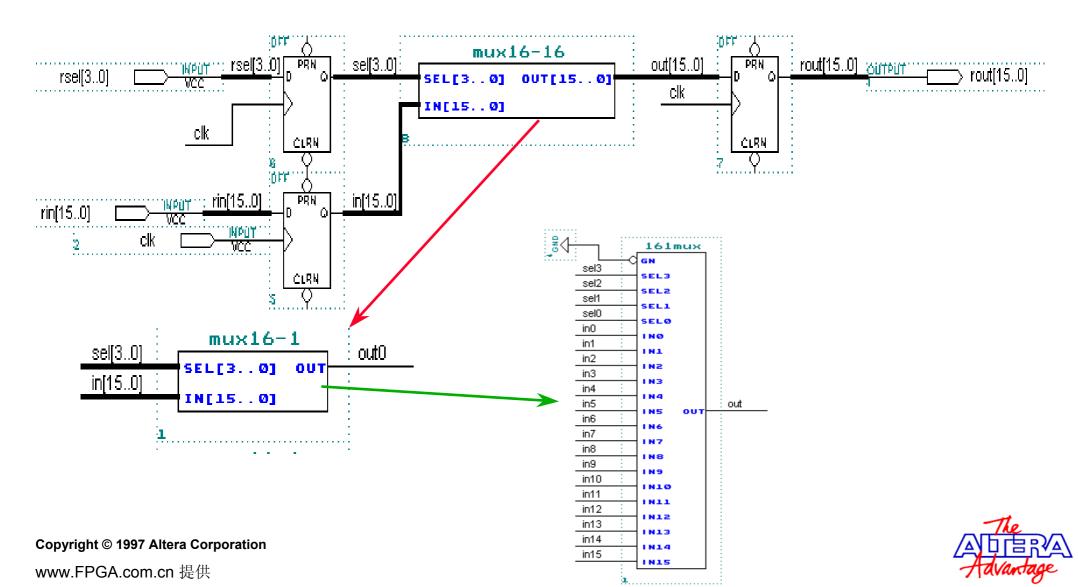

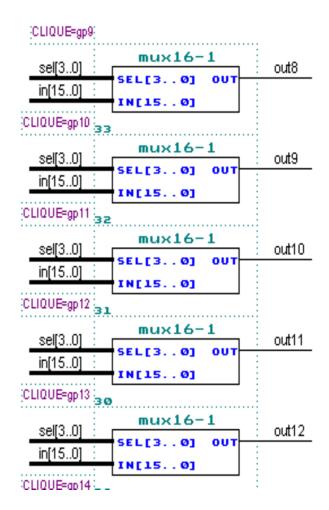

# **Apply CLIQUE to MUX16-16**

# Why?

- The 16x16 MUX is construct from 16 individual 16-to-1 MUX

- This 16 individual 16-to-1 MUX is no relationship with each other

- Apply CLIQUE to this 16x16 MUX means you force this 16 individual MUX place together

- Now this 16 individual 16-to-1 MUX somehow has relationship between each other through this CLIQUE application

- Is that CLIQUE is not GOOD?

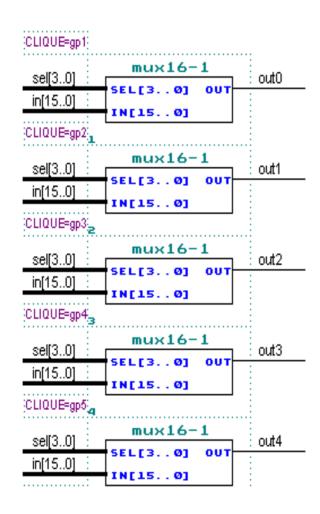

## **Apply CLIQUE to individual 16-1 MUX**

## **Use CLIQUE wisely**

- CLIQUE really help you to achieve HIGH SPEED design

- if and only if apply it correctly

- Apply CLIQUE ONLY to the logic which having relationship with each other

- Breakdown your big design to smaller sub-module design will easier for apply CLIQUE

- that is Floorplan in advance means for

## THINK BEFORE CLIQUE

# **Design Revolution**

- In the past, design is base on FUNCTIONAL partition

- address decoder, state machine 1, state machine 2 etc.

- Todays, we are facing with HIGH SPEED DESIGN

- High Speed Design need a good floor planning in advance

- CLIQUE is a powerful tools to control placement

**Good Floor Planning in advance + CLIQUE = HIGH SPEED DESIGN**

#### Conclusion

Apply CLIQUE at the whole design = No CLIQUE at all !!!!!!