-

-

-

zpjames1127 | 当前状态:在线

总积分:526 2026年可用积分:1

注册时间: 2006-08-15

最后登录时间: 2025-08-01

-

-

确定“Clock Ticks”或模拟时间

zpjames1127 发表于 2023/8/18 17:54:45 889 查看 3 回复 [上一主题] [下一主题]

手机阅读

桌面执行节点可以控制模拟时间,因此开发人员可以使用模拟I/O在开发计算机上执行期间更改关键点的激励。要成功使用此功能,需要测量FPGA VI完成所需的时间,或者需要以直观地知道完成所需时间的方式设计VI(例如,使用循环定时器来保证定时)。以下是测量完成FPGA VI所需时间的一些提示。

单周期定时循环

如果使用的是SCTL,则该循环中包含的代码始终需要参考时钟的一个时钟周期来执行,因此可以将时钟周期设置为1个时钟周期。如果有多个SCTL,请选择最快的时钟作为参考时钟。

带循环计时器的循环

在这种情况下,可以指定循环计时器的值(以刻度为单位)。如果循环计时器以毫秒或微秒为单位配置,请执行转换。例如,如果将循环定时器设置为10μs,请执行以下计算:

■Ticks=时钟(Hz)x时间(s)

■Ticks =40,000,000Hzx0.00001秒

■Ticks =400

因此,可以将桌面执行节点中的时钟周期输入配置为400个时钟周期。

没有循环计时器的循环

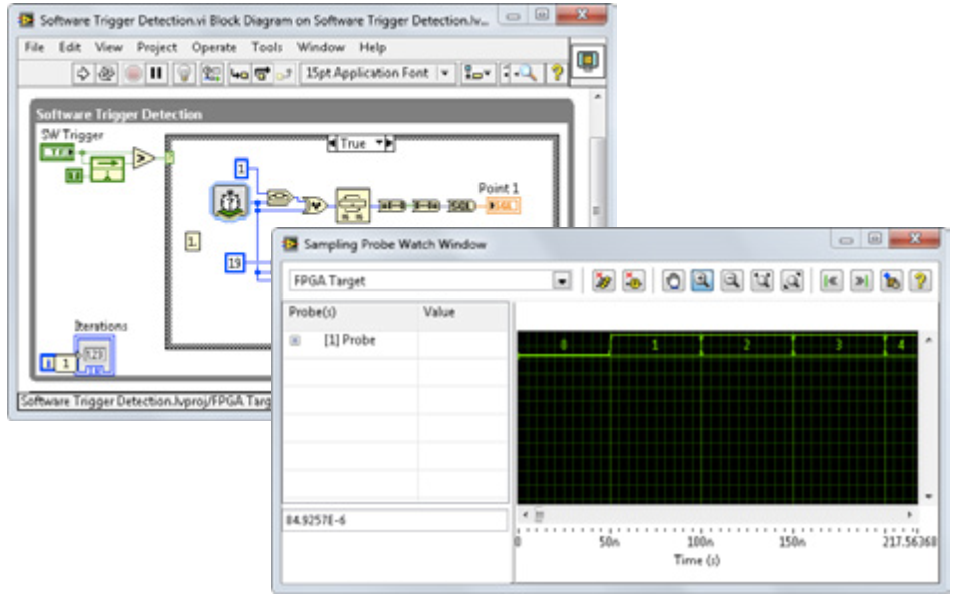

如果使用不包含任何模拟I/O(可能包含数字I/O)的While环路,则测量刻度数的最简单方法是使用采样探针。为此,请在While循环迭代终端上创建一个指标。右键单击连线并选择SamplingProbe?FPGA.。在仿真模式下运行VI一两秒钟,停止并查看采样探针窗口。在下面的示例中,可以看到While循环需要40MHz时钟的两个时钟周期来执行,根据采样探测窗口(每个时钟周期等于25ns)。对于这种情况,可以将时钟刻度输入设置为两个刻度。

注意:由于这是一个While循环,因此在仿真中测量的时钟周期数不一定等于在硬件中执行相同代码时产生的时钟周期数。但是,SCTL中的任何代码都可以保证循环准确。

图5.36.使用采样探测器测量每次迭代的时钟周期数

当循环以Delta-Sigma Module时钟的速率执行时

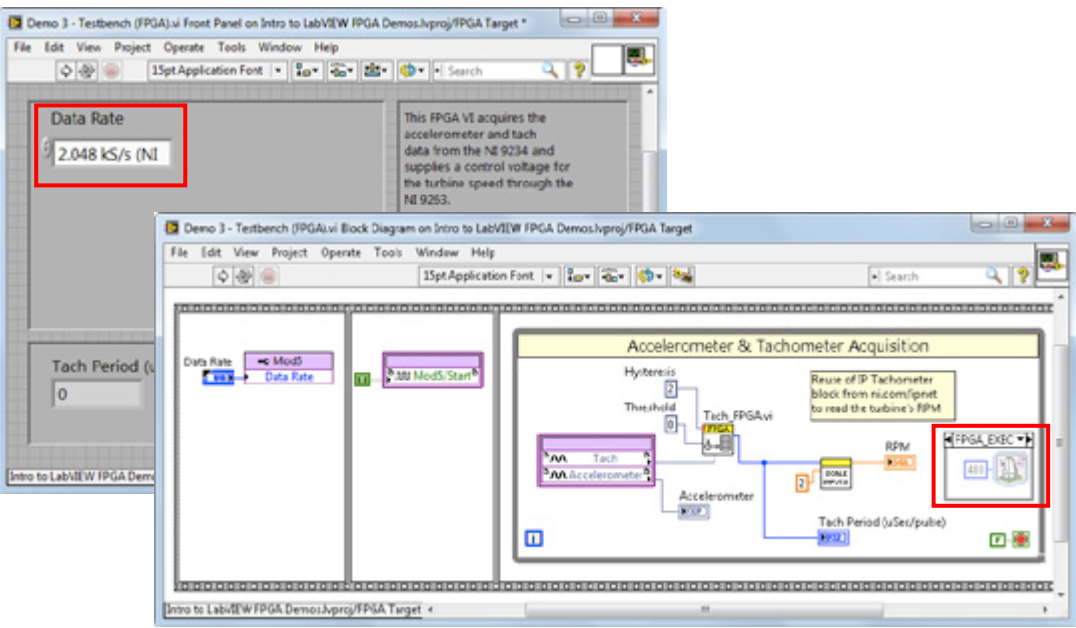

可能有一个以Δ-Σ模拟输入模块定义的速率执行的FPGA VI,例如图5.37所示示例中使用的VI。在仿真模式中,LabVIEW忽略来自这些属性节点的定时输入。因此,这些情况要求执行两个步骤:

1.通过添加相当于扫描速率的循环定时器来控制VI的仿真时序

2.将桌面执行节点中的时钟周期输入设置为与循环计时器输入的值相同的值

在此特定示例中,从转速表读取数据,模拟输入模块配置为以2.048kS/s或488μs的速率运行。第一步,需要将循环定时器添加到While循环中,并将其配置为488μs的循环速率。

图5.37.通过添加条件环路定时器来指定模拟时间。

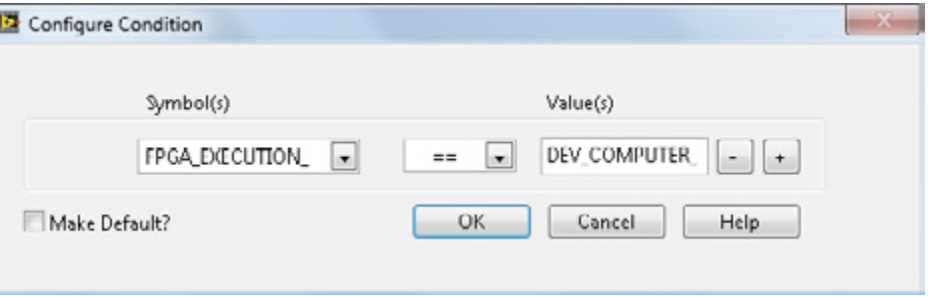

可以将循环定时器置于条件禁用结构中,以便仅在VI执行模拟模式时才调用它。使用以下值配置条件禁用结构:

■FPGA_EXECUTION_MODE==DEV_COMPUTER_SIM_IO

循环计时器应放置在此条件大小写中,默认大小写应为空。

图5.38.配置条件禁用结构

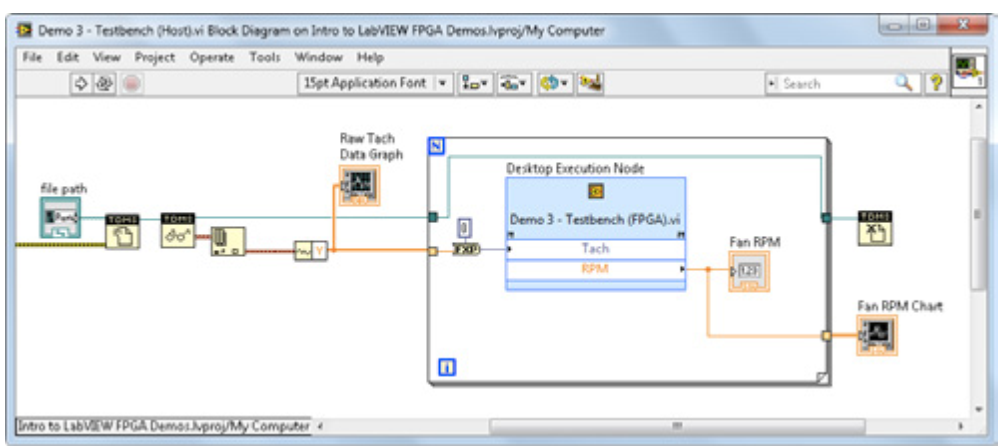

最后一步是在桌面配置节点中设置时钟周期输入。在此示例中,488μs等于19,531个时钟周期,因此将时钟时钟周期输入设置为19,531个时钟周期。

第3步:构建测试平台

成功配置桌面执行节点后,即可开始构建测试平台。在下面显示的示例中,记录的转速计数据从TDMS文件中读取,并写入称为Tach的模拟输入I/Onode。FPGA VI在仿真模式下执行,结果rpm显示在图表上。要验证转速表IP,可以查看从文件中读取的转速表数据和绘制到图表的转速表数据。

图5.39.创建测试VI并验证FPGA代码。