美国模拟器件公司 David Katz Rick Gentile Jorge Manguane

最近出现了一些兼备数字信号处理器(DSP)和微控制器(MCU)能力的处理器,从而为那些既要求典型的MCU功能又要求高性能信号处理功能的应用大开了方便之门。这类MCU的优势之一就是起到系统控制器的作用,通过以太网接口、USB接口和PCI等标准接口来协调各子系统的活动。因为许多信号处理器都包含了这样一些相同的接口,所以考虑一下系统的体系结构正在如何演进是很有意义的。本文将讨论一种DSP在一个基于PCI的单板计算机应用中起到系统控制器作用的实现方法。

PCI总线的开发是为了提供一种能轻松连接外围设备和台式计算机的高性能方法。这些外围设备包括图形子系统、磁盘控制器和I/O设备。PCI总线与CPU总线是分开的,但是仍然需要访问主存储器。该接口可以通过一个电桥连接至系统总线,该电桥允许它以独立于CPU时钟频率的固定频率运行。总而言之,PCI为关键的系统元件提供了一个高带宽的通道,以便在彼此之间传送数据。

随着嵌入式计算的出现,人们都希望以最低的成本设计出带有通用外围设备的不以PC为中心的计算平台。由于PCI的性能、可扩缩性和普遍性,使其成为一种自然的“通用标准”,用于连接大量已经使用的外围设备。

此外,通过标准接口将嵌入式处理器连接到比它们功能更强大的台式机处理器是很有利的,其驱动力是嵌入式应用的发展,例如,用户手持设备、销售点终端以及连接PC的工业自动化系统。PCI促进了模块嵌入式系统设计,从而允许多种外围设备能无缝地连接到一种通用总线。最后,这种方法降低了产品总材料成本并且增加了设计的重用,从而降低了开发带有嵌入式PCI接口的处理器的总风险。

系统体系结构的演进

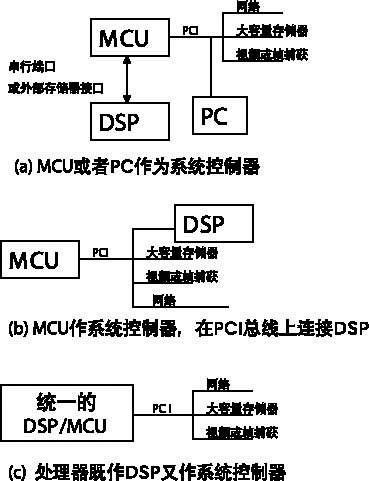

在MCU控制的系统中,DSP一般是充当协处理器。如图1(a)所示,这种配置中的MCU和DSP通常是通过高速的串行链路或者存储接口进行通信。MCU先把数据传递给DSP,然后DSP把处理过的数据传回给MCU,很可能还是通过同样的接口。对诸如音频处理这样的中低带宽应用来说,这种方式效果很好。但是在处理高带宽数据流时,这种方式就就无法胜任了,例如,原始视频流,很可能就要求超过25MB/s的数据传送速率,远远超过了传统的高速串行接口所能支持的8~15MB/s的速率。另外,如果MCU和DSP之间没有可用的专用存储接口,共享的存储器会降低总体性能,因为DSP在访问共享空间的同时也占用了MCU的外部存储器总线。

上述不利因素的结合导致了如图1(b)所示的排列。通过在DSP中集成PCI功能,该DSP可以简单地看作另一种置于由MCU主控的PCI总线另一端的“外围设备”。在这里,DSP起到“PCI设备”的作用。该PCI连接利用空闲的带宽来支持视频流速率,而且这种配置甚至允许该DSP作为一种“总线主控器”以便直接访问该PCI总线上的其他设备(例如网络和存储接口)。

随着系统成本压力进一步推动了设计的集成,如图1c所示的解决方案就更加理想。图中的处理器不是一个简单的DSP,而是一种结合了强大的DSP和MCU功能的信号处理器。因此,它可以作为系统控制器,能主控PCI总线并且减少了一个处理器,从而大大节省了总系统成本。ADSP-BF533 Blackfin媒体处理器正是具备这种功能的器件。

PCI接口的特点

为了便于下一步的讨论,先明确几个与PCI有关的关键术语。

● 主机与设备,主控器与受控器

PCI的主要特点之一就是对等通信。考虑到大多数的设备都支持一种“主控器”操作,随后设备就可以在彼此之间或者与系统主机(例如,图1(a)所示的MCU或PC)之间通信。在这种拓扑结构中,所有的设备,包括主机,都能作为一个特定PCI事务的主控器或者受控器。主机与设备的区别就在于主机可以在总线上配置各PCI代理并且提供总线仲裁。通过配置,各PCI代理(可以主控总线的设备)将彼此看成是一种存储映像设备的集合,可以通过在它们各自的存储器区域中发起数据传送来访问这些设备。每个PCI代理都可以对目标机(“受控器”)发起一次数据传送,从而成为该特定事务的总线主控器。

● 总线仲裁

在一些嵌入式应用中,当前的总线主控器可以不止一个,这时就需要一个PCI总线判决器。在嵌入式应用中利用一个小型的可编程逻辑电路(PLD)很容易实现这种功能(以前都由PC提供)。每个可能的总线主控器都有两条线(一条用于请求,一条用于授权)进入总线判决器。当一个总线主控器要求使用PCI总线时,必须在其设备请求线上申请。判决器来决定什么时候授予其总线使用权并在适当的时候通知其授权线。虽然PCI标准中没有规定具体的仲裁算法,但是要求有“一种公平的算法以防止死锁”。通常,可以采用一种简单的轮循方法来确保不会有某一个总线主控器独占总线。

● 性能

如果数据吞吐量性能很重要,那么突发传送是很关键的。PCI总线上的突发传送主要是由同一地址段接连发生至少两次数据传送而引起的。和其他的传送类型一样,一旦总线主控器接收到PCI总线的使用权,就要传送其起始地址和事务类型。在实际的PCI系统中,总线主控器和目标机必须都支持突发事务。例如,如果目标机只支持单一事务,性能就会极大降低,因为该总线主控器必须反复申请总线使用权并传送每个事务的地址。当总线主控器和目标机都支持突发事务时,该PCI上的带宽就能达到132MB/s(4B×33MHz)的最高吞吐量。

直接存储器存取(DMA)是提高接口中数据传送带宽的关键,因为它在传送数据时所需内核处理器的干预最小。这种采集或传送数据的设备可以利用其自带的DMA控制器,自动地从处理器来回传送数据。DMA通过利用PCI的突发能力来存取接口中的大块数据,从而极大地提高了性能。这种能力推动了诸如实时视频处理等应用的发展。

● 对多处理器系统的内在支持

通过用PCI总线连接多个嵌入式处理器,就能实现一个多处理器系统。采用这种直接的连接方式很容易就能使计算能力成倍增加。有了附加的数据总线以及每个处理器访问存储器的能力,就能处理数据流。采用这种方法,无须增加算法的编程复杂度就可以在每个处理器之间对数据进行分区。另外,即使是在视频吞吐速率,仍然有足够的可用空间用于与控制有关的传送开销

从系统控制器的角度看PCI

● PCI存储器模式

PCI协议使用基地址寄存器(BAR)为各设备分配存储器和I/O范围。在配置期间,主机会询问各个设备以便决定每个设备所需资源。如果主机可以提供所有这些资源需求,它就会在每个设备的存储器BAR和I/O BAR中写入相应的起始地址。然后,通过对其存储器或者I/O范围内发起一次传送就可以访问每个设备了。此外,每个PCI代理都可以访问总线上的所有其他代理。

ADSP-BF533是一个PCI设备,它有BAR0(存储器BAR)和BAR2(I/O BAR)两个寄存器,以及相应的屏蔽寄存器。这些屏蔽寄存器可用于指定每个区域所需要的存储数量。

因为主机是在其PCI存储器空间内为设备分配一个地址,所以该设备(在这里就是指BF533)需要将此地址映射到它的内部或者外部存储器空间中。对BF533来说,存储器空间包括芯片内的L2存储器以及外部的SDRAM和(或)异步存储器,并且I/O空间会映射到处理器的存储器映射寄存器(MMR)区域。在这些定义的引导下,一个内部事务就会被控制在适当的区域。

当ADSP-BF533作为给定事务的目标机(受控器)时可以应用上述讨论的方法。当它发起传送时,会在其PCI外部存储器BAR或者I/O BAR中写入它希望访问的代理地址。无论是对PCI存储器还是I/O空间的一次读或写都会发起一次以该PCI代理的存储器或者I/O区域为目标的事务。

在主机模式中,外发事务的发生方式与上面的描述类似。对内送事务(ADSP-BF533作为受控器)的方案稍微有些区别。在主机模式中,BF533不使用BAR寄存器,而是使用主机存储控制寄存器将其资源开放给外部代理。它可以接受或者不接受对其存储器和I/O空间的访问。在有些情况下,它还能指示那些开放资源还有多少可以被外部PCI代理访问。这就为保护关键的代码或者数据段免遭其他PCI代理的更改提供了一种机制。

● 在PCI存储空间中开窗口

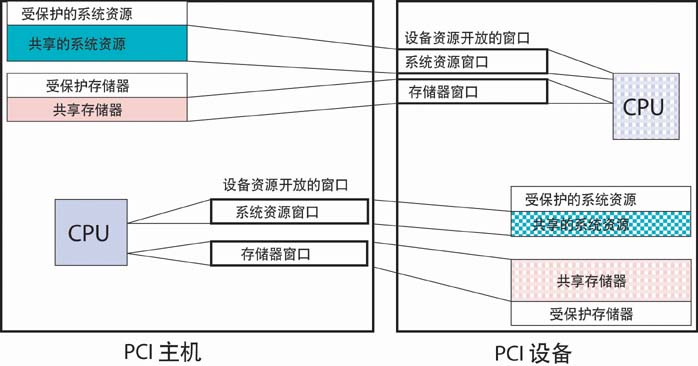

一旦初始化完成后,每个PCI设备都有对主机或总线上其他PCI设备“开放”的存储资源。这些存储资源可以包括内部存储器和外部存储器。例如,在BF533中,内部或者外部L2存储器中的“窗口”可以被PCI总线上的任何其他设备共享。然后每个总线主控器就可以直接访问这些开放的存储器空间,就像是在访问它自己的内部存储器一样。一旦主机完成了初始化进程,各设备之间的所有存储器地址都能被PCI接口翻译出来。

术语“窗口”用于表示该设备可能还有不允许别的总线主控器共享的其他受保护资源。这种开放的窗口清楚地表示了可以直接进行传送的存储资源。这种方法是很重要的,因为对任何给定设备都不需要内核处理器参与每一件事务。

图2的简单实例示出了主机中的窗口指向设备资源以及设备中的窗口指向主机资源。这就是允许单个的内核处理器能将外部资源当做简单的存储器地址来访问的机制。

通常采用邮箱中断方式来协调总线主控器与PCI设备之间的数据传送,这就使接收设备知道数据什么时候可用以及什么时候准备用于处理。

● 数据传送路径

BF533有一组专用的外部主控器总线,允许外部的总线主控器直接从(或对)内部的L2存储器或者芯片外的SDRAM传送数据而无需内核处理器的介入。另外,可以建立PCI映射以便允许访问某些系统资源,例如,共享的外围设备。上述每种数据传送方法都只需要不多的初始化代码。内核处理器只需要管理信号量以便指示什么时候可以交换数据,以及什么时候可以将数据从该系统中传送出去。

除了上述传送路径外,还有一种内部的存储器DMA控制器可以用于发起任一方向的数据传送。这种数据传送路径能支持外围设备间的突发传送。

在支持PCI的嵌入式媒体处理器上实现视频捕获

下面将给出一种能执行主机控制器和信号处理器任务的嵌入式媒体处理器的具体实例,目的是要说明一种带有集成PCI接口的嵌入式处理器是如何用在具有各种不同接口要求的系统中的。这里的重点是数据搬移以及接入许多基于PCI的主流外围设备的能力。因为安装PCI接口就跟安装存储器一样,所以通过把这些外围设备映射到一些存储器的位置就极大地简化了编程模式。初始化完成后,每个外围设备都会对主机处理器开放一个窗口用于双向的数据交换。

在本例中,采用Momentum Data Systems (MDS)公司的Eagle-35主板来迅速实现一个系统,该PCB的原理示意图参见图3和图4。Eagle-35是一个单板计算机(SBC)的主处理器,该SBC有4个内部PCI插槽,板内还包含了一个以太网控制器,并且连接到PCI总线,采用一个廉价的PLD实现5设备的PCI判决器。它还包括了一个可连接SDRAM内存模块的插座,可以提供128MB的外部存储器。

首先可以把一个视频画面捕获卡安装到其中一个PCI插槽中。利用照相机数据源或者视频源的多路复用流,可以一次把一帧的视频数据直接送入SDRAM。另外,每一路数据都可以直接进入外部存储器用于处理。为了说明清楚,假定有一个安全应用,它有一路输入的CIF视频流,从10MB/s数量级的数据压缩至KB/s数量级范围(具体取决于期望的压缩图像质量等级)。该视频画面捕获卡上的一个DMA控制器直接将数据传送到SDRAM中。因为BF533有一个双MAC/ALU的内核处理器,所以可以实时地完成每一输入帧的数据压缩。可以处理的压缩类型有好几种,包括MJPEG、MPEG-2以及MPEG-4。采用这些算法进行CIF格式的压缩仅消耗内核处理器资源的很小一部分。

PCI接口有多种方法可以将压缩后的数据从处理器传送出去。一种方法是利用以太网控制器把压缩数据流送到远程网络地点,另一种方法是利用一个IDE驱动器来保存视频,这两种方法都接受PCI数据流,这样就简化了需要的编程模式。因为BF533的DSP处理能力既支持编码也支持解码,所以压缩图像可以重新传回给同样的系统。

在SDRAM中可提供多个输入和输出帧的缓冲器,这些缓冲器采用一种反复的方式轮流保存数据。当一个输入缓冲器充满了来自视频捕获设备的数据时,另外一个缓冲器的数据正在被压缩。两个输出缓冲器允许输出方向的并行操作。当一个输出缓冲器充满了压缩数据时,另一个缓冲器中的数据可以被传送到IDE驱动器或者以太网接口中。

Eagle-35主板是一种ATX型的设备,所以适合于做一个PC机箱中的主板。为了方便访问,音频编解码接口等所有的附加接口都放到了电路板的外部。有了板内的编解码器,就可以完成音频的压缩以便匹配视频流。