众所周知,半导体(IC)芯片是在一颗晶片上,历经数道及其细微的加工程序制造出来的,而这个过程就叫做工艺流程(Process Flow)。下列我们就来简单介绍芯片生产工艺流程:

芯片工艺流程目录:

一、半导体晶圆工序前半部分,在硅基板上制造出晶体管等部件:

1、元件隔离、2、井道形成、3、栅极氧化及闸形成、4、LDD形成、5、侧壁间隔、6、源极与漏极、7、硅化物、8、介质膜、9、接触孔

二、 半导体晶元制造工序的后半部分,将在生产线前道工序(FEOL)制造的各部件与金属材料连接布线,以形成电路(芯易网注):

10、金属—1、11、金属—2

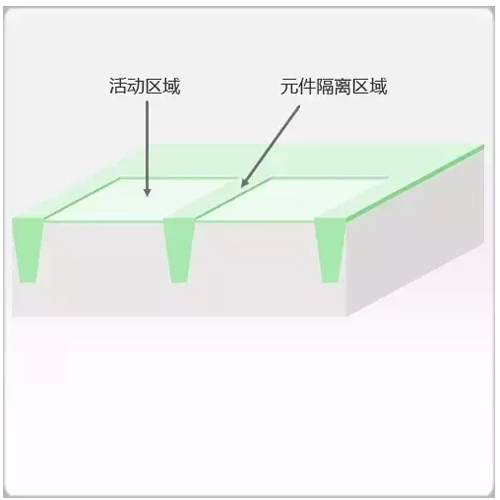

1、 元件隔离:

为保证每个在硅晶片的表面附近的晶体管能独立运行,要隔离晶体管的形成区域,以便阻止晶体管之间的相互干扰。

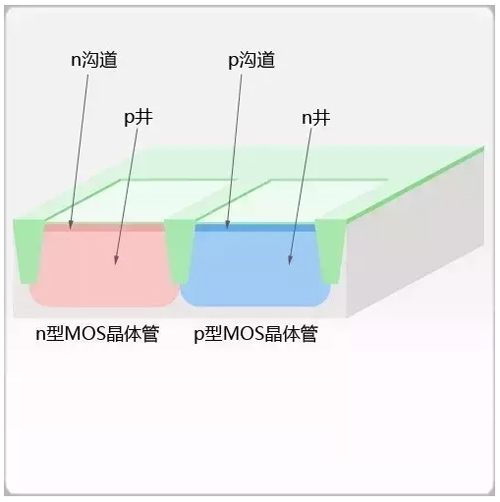

2、 井道形成:

在晶体管区域内掺入不同浓度、剂量的杂质,用来制作不同电压特征的晶体管。具体做法是给不同的晶体管区域,注入适量浓度的杂质((n型MOS:p井,n沟道;p型MOS: n井,p沟道);然后提取p型MOS晶体管和n型MOS晶体管。

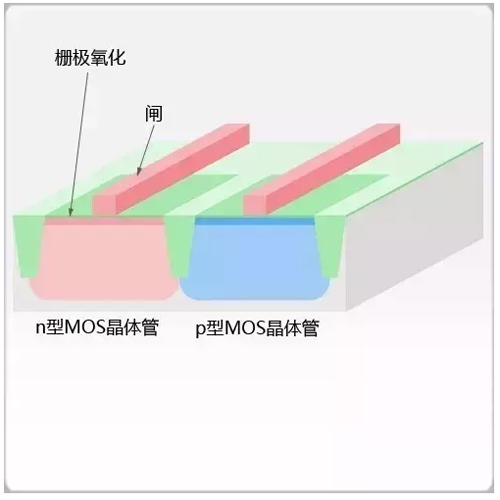

3、 栅极氧化及闸形成:

栅极氧化及闸形成是决定晶体管性能的关键工序,由于栅极氧化和闸形成的尺寸会影响晶体管的性能,所以需要在晶片表面均匀布上高密度的薄膜。再对光刻胶形成以及栅极蚀刻对尺寸进行严格的管理,利用CVD法来沉积多晶硅,形成栅电极。

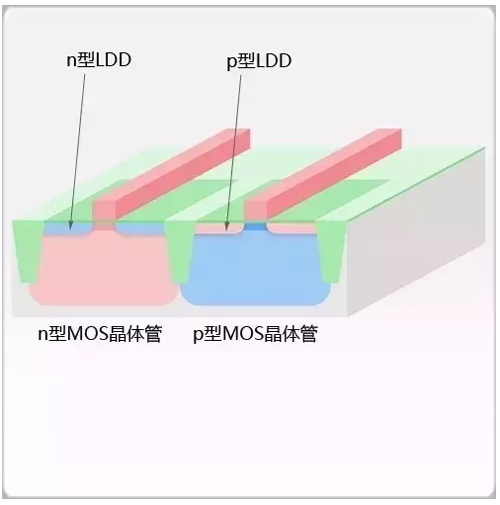

4、 LDD形成:

LDD(轻掺杂漏,Lightly Doped Drain)也被成为扩展,是为了避免微型化后,晶体管带来操作不利的影响(如速度变慢等)。p型LDD:在p型MOS的区域内加入p型杂质(如硼等);n型LDD:在n型MOS的区域内加入n型杂质(如磷、砷等)。

5、 侧壁间隔:

侧壁间隔是对上述LDD、栅极和下面将提到的源极、漏极的硅化,起到承上启下的作用。所以需要栅极的两端(水平方面)的壁部形成氧化膜。侧壁蚀刻是在氧化膜上实施异向性(垂直方向)的蚀刻,使得氧化膜仅残留在栅极的侧壁;侧壁氧化膜则是在整个晶片表面形成氧化膜。

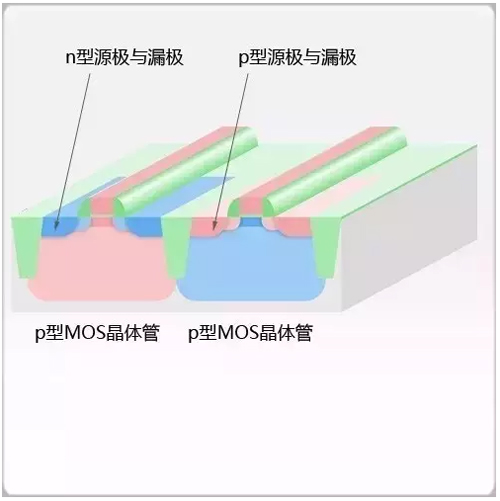

6、 源极与漏极:

通常情况下,p型MOS领域会形成源极,n型MOS领域内会形成漏极,由于晶体管形状相同、水平也对称,所以决定电源连接方向的是源极与漏极。n型源极与漏极的加工方法:n型MOS区域内掺入n型杂质(如磷,砷等);p型源极与漏极的加工方法:p型MOS区域内掺入p型杂质(如硼等)。

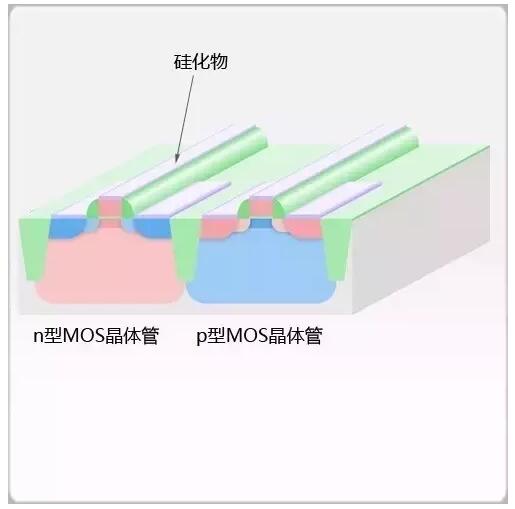

7、 硅化物:

将MOS的栅极(多晶硅)、源极、漏极(硅),与金属的化合物一起硅化之后,MOS的三个电极滋生的电阻就会降低,对金属布线层的电阻也随之降低。硅化是通过自对准硅化(化学蚀刻),选择性地去除钴薄膜。

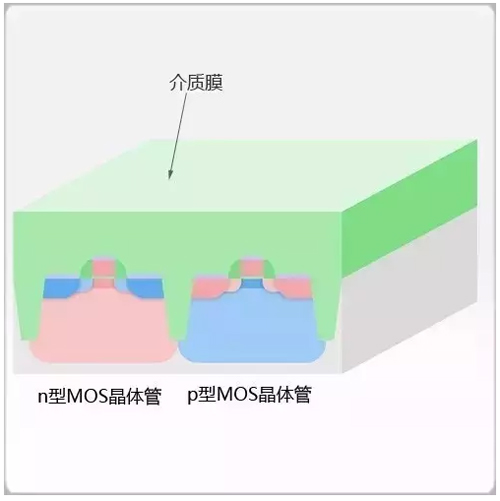

8、 介质膜:

为使晶体表面凹凸不平的部分变得平坦,必须对介质膜进行抛光(介质膜抛光);再通过CVD法形成厚的硅氧化膜(介质膜沉淀);这是连接晶体管等元件的布线流程。

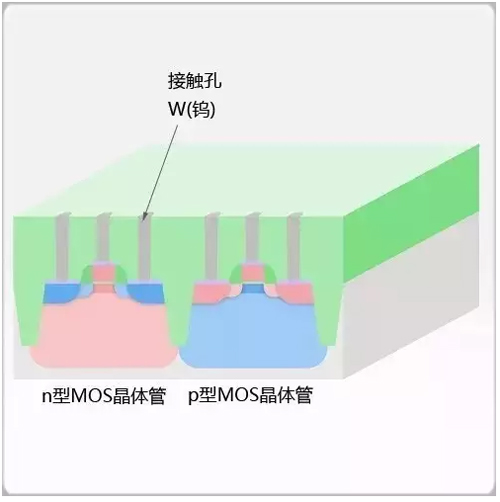

9、 接触孔:

接下来是对介质膜进行开孔(接触孔)并填充W(钨),这是为了将栅极、源极、漏极等三个电极透过介质膜上的金属层连接在一起。插件钨填充:填充接触钨;并对插件钨和晶体管的介质膜进行抛光,把多余的钨去除,使钨只存放在接触孔的内部。

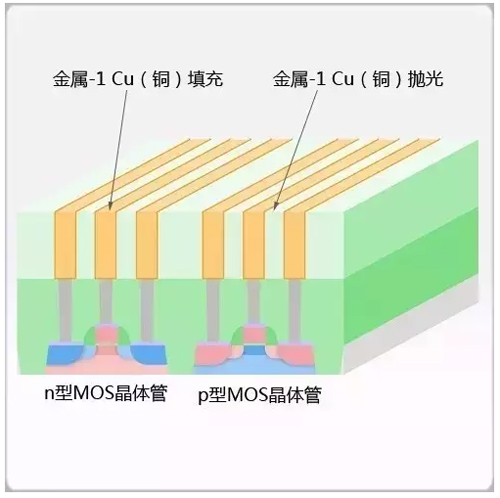

10、金属—1:

晶体管形成介质膜后,挖沟槽填充铜(Cu),这就被称为single damascene(单镶嵌)。金属—1铜(Cu)填充指的是用电镀的方法向沟槽内填充铜(Cu);金属—1铜(Cu)抛光指的是在介质膜表面抛光,去除表面的铜(Cu),让铜(Cu)只存放在沟槽内部。

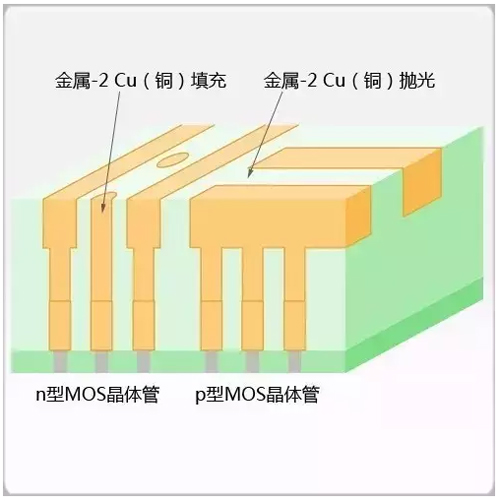

11、 金属—2:

在形成介质膜的晶体管上挖沟槽,填充铜(Cu),通过同时向孔和沟槽填充铜(Cu)的方式叫dual damascene(双镶嵌)。金属—2铜(Cu)填充指的是用电镀的方法向沟槽内填充铜(Cu);金属—2铜(Cu)抛光指的是在介质膜表面抛光,去除表面的铜(Cu),让铜(Cu)只存放在沟槽内部。