32位LPC1754FBD80ARMCortex-M3微控制器;ARMCortex-M3的MC;高达512KB的闪存和64KB的SRAM,带有以太网,SB2.0主机/设备/OTG,CA。

LPC1759/58/56/54/52/51手臂Cortex-M3基于微控制器的嵌入式应用程序有一个高水平的集成和低功耗。手臂Cortex-M3下一代核心,提供系统的改进,如增强调试功能和更高层次的支持块集成。

LPC1758/56/57/54/52/51操作在CP频率100MHz。的LPC1759运作在CP频率120MHz。手臂Cortex-M3CP结合了管道强度和使用一个哈佛架构与独立的地方指令和数据总线以及第三个总线外设。手臂Cortex-M3CP还包括一个内部预取单位支持投机分支。

的外围补LPC1759/58/56/54/52/51包括512kB的闪光记忆,64kB的数据存储器,以太网MAC,SB设备/主机/OTG接口,摘要介绍通用DMA控制器,4art,2通道,2SSP控制器,SPI接口,2i2c总线接口,2-ipt+2-otptI2S-bs接口,6通道12位ADC,10位DAC,电动机控制脉宽调制、正交编码器接口,4目的计时器,6-otpt通用PWM,超低能耗的实时时钟(RTC)单独的电池供应,52通用I/O引脚。

LPC1754FBD80特性和好处

手臂Cortex-M3处理器,运行在100MHz的频率

(LPC1758/56/57/54/52/51)或120 MHz(LPC1759)。一个内存保护单元

(微控制器)支持包括八个地区。

手臂Cortex-M3内置嵌套矢量中断控制器(VIC)。

512 kB内存芯片上的flash编程。增强的闪存加速器

使高速120MHz操作零等待状态。

在系统编程(ISP)和应用内编程(IAP)通过片上

LPC1754FBD80引导装载程序软件。

LPC1754FBD80片上存储器包括:

32 kB的SRAMCP与本地代码/数据总线的高性能

CP访问。

两个/一个16kB SRAM块更高的吞吐量的单独的访问路径。

这些存储器块可以用于以太网(仅LPC1758),SB,DMA

内存,以及通用CP指令和数据存储。

八频道通用DMA控制器(GPDMA)AHB多层

矩阵可用于SSP,I2S-bs、ART、模拟数字

数模转换器外设,定时器信号匹配,

内存到内存传输。

多层AHB互连矩阵提供了一个单独的每个AHB总线主人。

AHB大师包括CP、通用DMA控制器,以太网MAC

(仅LPC1758),SB接口。这种互连提供了交流

没有仲裁的延迟。

分裂APB总线允许高吞吐量和CP和DMA之间的几个摊位。

串行接口:

LPC1758只有,以太网MACRMII接口和专用DMA

控制器。

SB 2.0全速设备/主机/OTG与专用DMA控制器和控制器

芯片上的体育设备、主机和OTG功能。LPC1752/51包括SB

设备控制器。 主机,OTG功能。LPC1752/51包括SB

设备控制器。

四个art分数波特率一代,内部FIFO和DMA的支持。

一个ART调制解调器控制I/ O和rs - 485 / eia - 485支持,和一个ART

已经发送的支持。

可以2.0 b控制器有两个(LPC1759/58/56)或(LPC1754/52/51)通道之一。

SPI与同步控制器系列,全双工通信

可编程数据长度。

两SSP与FIFO控制器和多协议功能。SSP的接口

可以用于GPDMA控制器。

两个i2c总线接口支持快速模式的数据率400kbit / s

多个地址识别和监控模式。

LPC1759/58/56只有,i2(Iter-IC声音)对数字音频输入或接口

输出,与部分速率控制。I2S-bs接口可以使用

GPDMA。I2S-bs接口支持电话和四线传输和数据

接收以及主时钟输入/输出。

LPC1754FBD80其他外围设备:

52通用I /O(GPIO)针可配置的引体向上/向下电阻。所有

GPIOs支持一个新的、可配置的明渠操作模式。的块通过多层AHB总线访问的快速访问和位于内存中这样,它支持Cortex-M3条带和通用使用DMA

控制器。

12位模数转换器(ADC),输入多路复用中六针,转化率高达200千赫,多个结果寄存器。12位ADC可以被用于GPDMA控制器。

LPC1759/58/56/54只,10位数模转换器(DAC)

专用转换定时器和DMA的支持。

四个通用定时器/计数器,共有三个捕获输入和10

比较输出。每个定时器块有一个外部计数输入。特定的计时器事件可以选择生成DMA请求。

一个电机控制PWM对三相电机控制的支持。

正交编码器接口,可以监视一个外部正交编码器。

一个标准PWM与外部计数/定时器块的输入。

实时时钟(RTC)与一个单独的域和专用的清债信托公司振荡器。RTC块包括20字节的电池备份寄存器。

看门狗定时器(WDT)。可以定时从内部WDTRC振荡器,RTC振荡器或APB时钟。

手臂Cortex-M3系统计时器,包括外部时钟输入选项。重复中断定时器(RIT)提供可编程和重复的中断。

每个外围都有自己的时钟分频器进行进一步的电能节约。

JTAG标准测试/调试接口兼容现有的工具。串口线调试和串行线跟踪端口选项。

仿真跟踪模块允许非侵入性的,高速的实时跟踪指令执行。

集成PM(电源管理单元)自动调整内部监管机构

最小化能耗在睡眠中,深度睡眠,省电,深

省电模式。

四个减少权力模式:睡眠、深度睡眠省电,省电。

单3.3 V电源(2.4V至3.6 V)。

可配置一个外部中断输入边缘/敏感水平。所有在端口0和别针端口2可以作为边缘敏感的中断源。

屏敝中断(敝中断)的输入。

唤醒中断控制器(WIC)允许CPU自动醒来可能发生的任何优先级中断,而时钟停在深度睡眠,省电,省电模式。

处理器唤醒从省电模式通过任何中断期间能操作省电模式(包括外部中断,RTC中断,USB活动,以太网唤醒中断(仅LPC1758),CA总线活动,港口0/2销中断,敝中断)。

警戒灯火管制与单独的阈值检测中断和强制复位。

加电复位(运动)。

晶体振荡器的工作范围1MHz到25兆赫。

4MHz内部RC振荡器削减1%的准确率,可以用作系统时钟。

锁相环允许CPU运行到最大CPU速度不需要高频晶体。可能从主振荡器运行,内部RC振荡器,或RTC振荡器。

USB锁相环为了增加灵活性。

代码阅读与不同的安全保护(CRP)的水平。

独特的设备序列号识别目的。

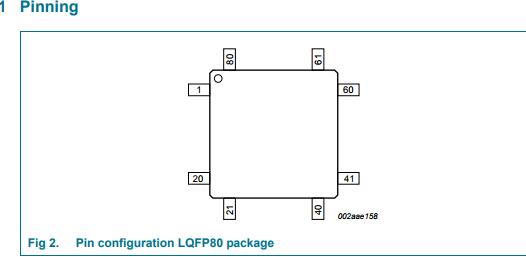

提供80 -销LQFP包(12毫米12毫米-1.4毫米)