F2803x短笛系列微控制器提供的力量C28x?核心和控制律加速器(CLA)加上高度集成控制外围设备在低大头针计数装置。这个家庭与先前的C28x-based code-compatible代码,以及提供一个高水平的模拟集成。

内部电压调整器允许单一铁路操作。增强了HRPWM模块允许dual-edge控制(调频)。模拟比较器与内部已经添加了10位引用可以直接路由控制PWM输出。

ADC的从0到3.3 - v转换固定满刻度范围和支持ratio-metric VREFHI / VREFLO引用。的ADC接口已经优化了低开销/延迟。

TMS320F28035PNT原子操作

快速中断响应和处理

统内存编程模型代码效率(在C/c++和组装)可编程控制律加速器(CLA)——32位浮点数学加速器

没有权力测序要求

集成的上电复位和暗光重置

低功率

没有模拟的支持

时钟:

两个内部Zero-pin振荡器

芯片上的晶体振荡器/外部时钟输入

动态锁相环比率变化支持看门狗定时器模块

失踪的时钟检测电路

45单独编程,

多路复用GPIO管脚输入过滤

外设中断扩张(派)块,支持所有外围中断

三个32位CPU计时器

在每个ePWM独立的16位定时器

模块

片上存储器

闪,SARAM OTP,引导ROM可用128位安全锁键/

保护安全的内存块

防止固件逆向工程串口设备

个sci(UART)模块

两个SPI模块

个Inter-Integrated-Circuit(12 c)总线

个当地的互连网络(林)总线个增强控制器区域网络(eCAN)总线

TMS320F28035PNT高级仿真功能

分析和断点功能

通过硬件实时调试

TMS320F28035PNT介绍

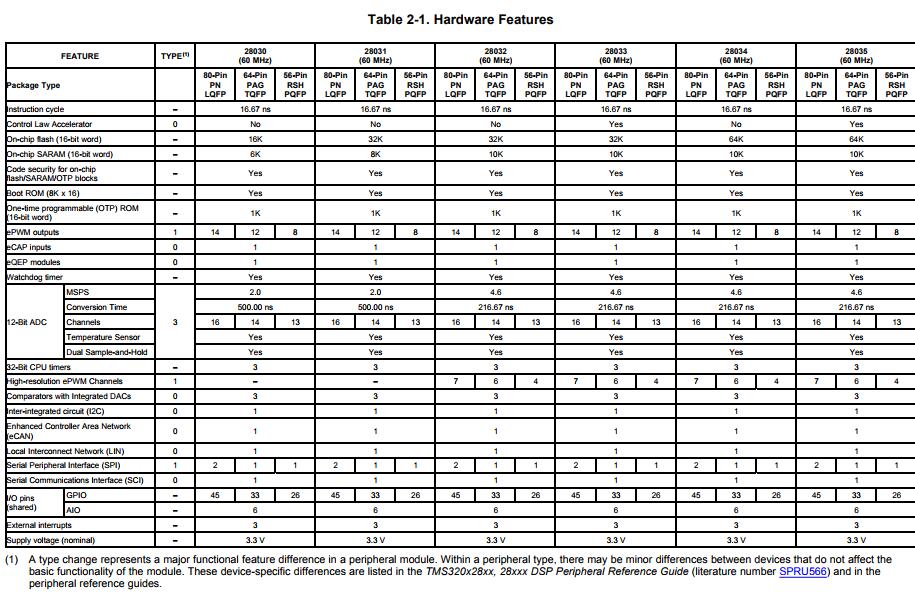

表2 - 1列出了TMS320F2803x设备的特性

强调

高效32位CPU(TMS320C28xTM)60mhz设备

个3.3v供应

接通电源的集成和暗光重置两个内部Zero-pin振荡器

45多路复用GPIO管脚

三个32位CPU计时器

芯片上的Flash,SARAMOTP存储器

代码安全性模块

串口设备

(SCI/SPI/I2C/林/eCAN)

增强控制外围设备

增强型脉冲宽度调制器(ePWM)高分辨率PWM(HRPWM)

增强捕捉(eCAP)

增强正交编码器脉冲(eQEP)

模拟-数字转换器(ADC)

芯片上的温度传感器

比较器

56-Pin,64针,64针包

高效32位CPU(TMS320C28xTM)60MHz(16.67挪威标准周期时间)

1616和32x32MAC操作

16x16双MAC

哈佛总线架构

TMS320F28035PNT请注意,一个重要的通知关于可用性标准保修,在德克萨斯州的关键应用程序中使用仪器半导体产品和免责声明出现在这个数据表。

2短笛,TMS320C28x C28x、TMS320C2000、代码作曲家工作室,XDS510,XDS560是德州仪器公司的商标。

3其他所有商标是他们的各自的主人的财产。

TMS320F28035PNT信号的描述

表2 - 2描述了信号。除了JTAG别针,默认的函数重置,除非另有提及。列出的外围信号下备用功能。一些外围功能可能不会在所有设备。详情见表2 - 1。输入不是5 v宽容。GPIO管脚都是I / O / Z和有一个内部减速停车,可以有选择地启用/禁用per-pin基础上。此功能只适用于的别针。PWM的引体向上针不启用复位。其他GPIO管脚的引体向上复位后启用。AIO针做的没有一个内部减速停车。

注意:当使用片上为VREG,GPIO19,GPIO34,GPIO35,GPIO36 GPIO37,GPIO38针可以在启动故障。如果这是不可接受的应用程序中,可以提供1.8 V外部。

没有power-sequencing要求当使用外部供应1.8 - v。然而,如果3.3 - v晶体管电平移动输出缓冲区的I / O引脚驱动前1.9 - v晶体管,它是可能的输出缓冲区打开,导致故障发生在销的力量向上为了避免这种行为,权力VDD针之前或同时VDDIO别针,确保前的VDD针已达到0.7 V VDDIO针达到0.7 V。