应用程序部分

LMV7219是一个具有内部滞后的单电源比较器,传播延迟7ns,电源仅1.1mA当前。

LMV7219具有典型的输入共模电压地面以下-0.2V到VCC以下1V的范围。

这个差分输入级是一对PNP晶体管,因此,输入偏压电流从设备流出。如果输入信号低于负共模限值,由基板和PNP的底部将打开,导致输入增加偏压电流。

如果其中一个输入高于正共模限制,输出仍将保持正确的逻辑电平只要其他输入保持在共模范围内。

但是,传播延迟会增加。当两者都输入超出共模电压范围,电流饱和发生在输入阶段,输出变为不可预知的。

传播延迟不会随着差分输入电压大。然而,大的差别应避免电压高于电源电压。

防止输入级损坏。

LMV7219M5电路布局和旁路

LMV7219需要高速布局。遵循这些布局指导方针:

1.电源旁路是关键,将提高稳定性以及瞬态响应。去耦电容器0.1μF陶瓷应尽可能靠近V+引脚。可能需要额外的2.2μF钽电容器。

为了降低噪音。

2.保持所有导线短接,以减少杂散电容和导线电感。它还将最小化不必要的寄生反馈在比较器周围。

3.设备应直接焊接到PC板上。

而不是使用套接字。

4.使用具有良好的、未破损的低电感的PC板地平面。确保接地路径低阻抗,尤其是当更大的水流。

5.输入记录道应远离输出记录道。这个可以通过在输出和输入。

6.在设备下运行接地跟踪直到旁路保护输入和输出的电容器。

7.当输入信号移动缓慢,1000pF或以下的小电容器可以置于输入之间。它还可以帮助消除振荡在过渡区。但是,这个电容器可以当源阻抗为低。

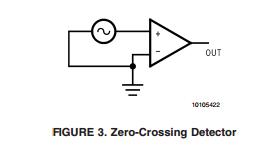

过零检测器反相输入接地,不反相输入连接到100MVP-P信号。作为非反相输入处的信号穿过0V,比较器输出更改状态。