描述:SSI CMOS四路异或和NOR门;

互补金属氧化物半导体集成电路四排“或”和“或”门MC14070B Quad Exclusive或Gate和MC14077B Quad专用或非门由MOS P通道和单块集成电路中的n通道增强模式器件结构。这些互补的MOS逻辑门是主要用途如果需要低功耗和/或高噪声抗扰度。

MC14070BDR2G特征

电源电压范围=3.0 Vdc至18 Vdc

所有输出缓冲

能够驱动两个低功率TTL负载或一个低功率

额定温度范围内的肖特基TTL负载

所有输入端的双二极管保护

MC14070B替换CD4030B和CD4070B型

MC14077BCD4077B型的替代品

提供无铅包装

超过最大额定值的应力可能会损坏设备。最大评级仅为压力评级。功能操作高于推荐值不暗示操作条件。暴露在高于推荐的操作条件可能会影响设备的可靠性。

MC14070BDR2G温度降额:

塑料“P和D/DW”包装:65C至125C的-7.0 mw/c该装置包含保护电路,以防止因高压而损坏。

静电电压或电场。但是,必须采取预防措施以避免任何高于最大额定电压的电压的应用高阻抗电路。为了正确操作,应限制VIN和VOUT到范围vss(VIN或VOUT)vdd。

未使用的输入必须始终与适当的逻辑电压水平相关联。

(例如,VSS或VDD)。未使用的输出必须保持打开状态。

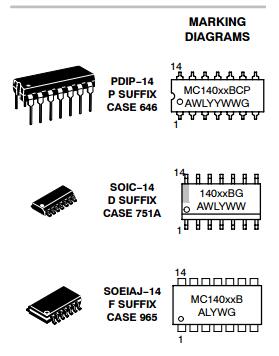

包装尺寸

笔记:

1.尺寸和公差符合ANSI1450万日元,1982年。

2.控制尺寸:毫米。

3.尺寸D和E不包括模具闪光或突起,并测量在分模线。模具闪光或突出物不得超过0.15(0.006)每边。

4.终端编号显示用于仅供参考。

5.导程宽度尺寸(B)没有包括Dambar突出物。允许拦污栅凸出量应为0.08(0.003)总宽度超过导程宽度最大材料条件下的尺寸。

Dambar不能位于下方半径或脚。最小空间突出物和相邻导线之间为0.46(0.018)。