简短描述

MSP430F5329IPN中央处理器

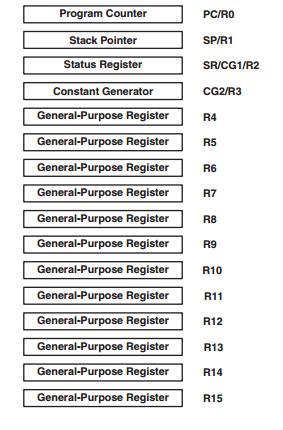

MSP430 CPU具有16位RISC架构,对应用程序高度透明。所有操作,

除程序流指令外,作为寄存器操作与七个寻址一起执行。

源操作数的模式和目标操作数的四种寻址模式。

CPU与16个寄存器集成,减少了指令执行时间。要注册的寄存器

操作执行时间是CPU时钟的一个周期。

其中四个寄存器r0到r3专用于程序计数器、堆栈指针、状态寄存器和常量。

分别是发电机。其余的寄存器是通用寄存器。

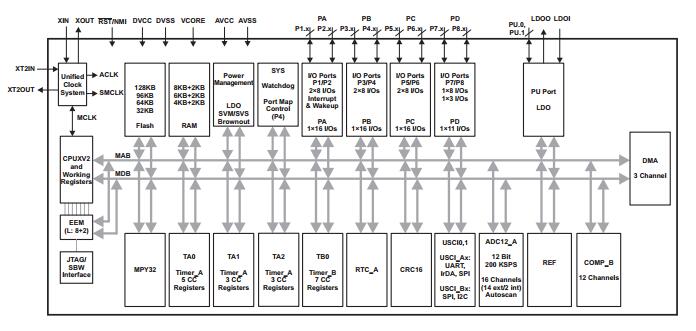

外围设备使用数据、地址和控制总线连接到CPU,可以用所有

MSP430F5329IPN说明。

指令集由原来的51条指令组成,有三种格式和七种地址模式。

扩展地址范围的附加说明。每个指令都可以操作字和字节数据。

描述:混合信号微控制器;

MSP430F5329IPN特征

低电源电压范围:1.8 V至3.6 V

超低功耗

激活模式(AM):

所有系统时钟激活

290 A/mhzat8 MHz,3 V,闪存程序

执行(典型)

150 A/mhzat8 MHz,3 V,RAM程序

执行(典型)

一待机模式(lpm3):

实时时钟与水晶,看门狗,

以及供应主管,全面运作

RAM保持,快速唤醒:

1.9 AAT2.2V,2.1 AAT3V(典型)

低功率振荡器(VLO),概述

专用计数器、看门狗和电源

主管操作,完整RAM

保留,快速唤醒:

1.4 AAT3 V(典型)

关闭模式(LPM4):

完整RAM保留,供应主管

可操作,快速唤醒:

1.1 AAT3 V(典型)

停机模式(LPM4.5):

0.18 AAT3V(典型)

从待机模式唤醒3.5秒

MSP430F5329IPN(典型)

16位RISC架构,扩展内存,

最高25兆赫系统时钟

灵活的电源管理系统

可编程的全集成LDO

调压铁心电源电压

一。电源电压监控,

和灯火管制

MSP430F5329IPN统一时钟系统

–频率的FLL控制回路

稳定

–低功率/低频内部时钟

源(VLO)

-低频修剪内部参考

来源(参考)

–32 kHz手表晶体(XT1)

–高达32兆赫的高频晶体

(XT2)

16位定时器TA0,定时器_ua带5个

捕获/比较寄存器

.16位定时器TA1,定时器。A加3

捕获/比较寄存器

16位定时器TA2,定时器A和3

捕获/比较寄存器

16位定时器tb0,定时器_uub,带7个

捕获/比较阴影寄存器

.2通用串行通信

MSP430F5329IPN接口

-USCL A0和USCL A1各支持

一。增强的UART支持

自动波特率检测

-IRDA编码器和解码器

-同步SPI

一USCI b0和USCI b1各支持

12CTM

一同步SPI

集成3.3-V电源系统

12位模数转换器

内部参考、样品和保存,以及

自动扫描功能

比较器

支持32位的硬件乘法器