以前在UDMA方式下也调试过出现数据CRC错误的问题,大致可以分为两类:1. 数据的建立、保持时间有问题;2. UDMA的中止协议处理不当,引发一次无效数据传输,进而导致主机与硬盘计算的CRC结果不一致。

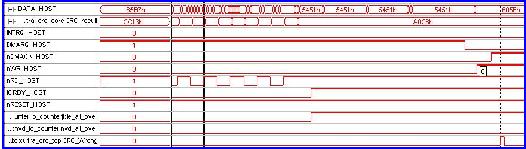

在SignalTap II下捕获的波形如下,采样周期单位10ns:

该波形显示的是一次主机UDMA写操作数据传输完毕时发生的CRC错误。位于波形右侧的trigger就设定在CRC错误被检出时。在波形开始部分,显示的是该次数据传输最后几个字的传输波形。从光标处可以看出,主机驱动的16位数据毛刺很多,数据的建立时间无法保证。16位信号展开后的波形如下图:

尝试采用

只得采用示波器观察部分数据总线,进而发现部分数据总线的电平有问题,主机驱动的0、1信号均无法顺利达到判决电平,存在ramp形式的波形(阶梯状上升或下降)。由此怀疑是设备端PCB的信号完整性或电源完整性有问题,尝试在电源之间加入电容仍然不能解决该问题。解决该的问题似乎只能重新制板。

在FPGA与PATA数据总线接口之间有串接的匹配电阻。为了进一步确认信号完整性问题,决定在该串联电阻前后观察信号波形。由此导致了该问题的解决。

通过观察该电阻前后的信号波形,没有发现波形形状上的差异,而发现在该电阻前后存在0.3V的电压差。进一步分析显示,在该电阻上有较大的电流流过,该电流导致了压降。

在正常的电路中,当主机驱动信号时,FPGA的相应引脚应该处于高阻状态,没有拉电流和灌电流,只有这样才能正确读取主机驱动的信号。但是在当前情况下,原本应该处于高阻状态的FPGA引脚却流过了较大的电流。该现象表明,FPGA内部的三态逻辑存在问题,不能正确产生高阻状态。进一步分析相应的HDL程序,发现在该条件下,确实存在不正确的电路行为,导致高阻状态不能出现在引脚上。修改该问题后,示波器上观察不到异常现象,UDMA主机写传输表现正常。

导致该问题分析方向错误的一个原因是,该错误电路在某一型号的主板上工作正常,长期测试稳定,与一款SATA桥接芯片连接工作正常,只是在兼容性测试中发现在特定主板上存在该问题。这一现象使我得出了FPGA内部不存在逻辑错误的结论。找到问题原因后,这一现象也得到了解释:由于总线驱动冲突的存在,总线上的电平受到串联匹配电阻的影响,该电阻起到了分压作用(还有限流作用),在某些主板上,对PATA接口的驱动电压较高,经分压后仍然能够达到正确的判决电平,所以测试通过,在某些主板上,由于南桥芯片的设计不同,驱动电压较低,该问题就表现出来了。